PCB设计中,晶振选型及布局注意事项

晶振,老生常谈的话题。在往期文章中,小编对晶振从各大方面进行过讲解,如PCB板上配备哪些晶振。而在本文中,将同大家一同探讨如何进行PCB晶振设计。如果你对本文将要讨论的晶振问题存在一定兴趣,不妨继续往下阅读哦。

我们常把晶振比喻为数字电路的心脏,这是因为,数字电路的所有工作都离不开时钟信号,晶振直接控制着整个系统,若晶振不运作那么整个系统也就瘫痪了,所以晶振是决定了数字电路开始工作的先决条件。

我们常说的晶振,是石英晶体振荡器和石英晶体谐振器两种,他们都是利用石英晶体的压电效应制作而成。在石英晶体的两个电极上施加电场会使晶体产生机械变形,反之,如果在晶体两侧施加机械压力就会在晶体上产生电场。并且,这两种现象是可逆的。利用这种特性,在晶体的两侧施加交变电压,晶片就会产生机械振动,同时产生交变电场。这种震动和电场一般都很小,但是在某个特定频率下,振幅会明显加大,这就是压电谐振,类似于我们常见到的LC回路谐振。

作为数字电路中的心脏,晶振在智能产品中是如何发挥作用的呢?以智能家居如空调、窗帘、安防、监控等产品来说,都需要无线传输模块,它们通过蓝牙、WIFI或ZIGBEE等协议,将模块从一端发到另一端,或直接通过手机控制,而晶振就是无线模块里的核心元件,影响着整系统的稳定性,所以选择好系统使用的晶振,决定了数字电路的成败。

由于晶振在数字电路中的重要性,在使用和设计的时候我们需要小心处理:

1、晶振内部存在石英晶体,受到外部撞击或跌落时易造成石英晶体断裂破损,进而造成晶振不起振,所以在设计电路时要考虑晶振的可靠安装,其位置尽量不要靠近板边、设备外壳等。

2、在手工焊接或机器焊接时,要注意焊接温度。晶振对温度比较敏感,焊接时温度不能过高,并且加热时间尽量短?

合理的晶振布局可以抑制系统辐射干扰

一、问题描述

该产品为野外摄像机,内分核心控制板、sensor 板、摄像头、SD 存储卡和电池五部分组成,外壳为塑胶壳,小板仅有两个接口:DC5V 外接电源接口和数据传输的USB 接口。经过辐射测试发现有33MHz 左右的谐波杂讯辐射问题。

原始测试数据如下:

二、分析问题

该产品外壳结构塑胶外壳,是非屏蔽材料,整机测试只有电源线和USB 线引出壳体,难道干扰频点是由电源线和USB 线辐射出来的吗?故分别作了一下几步测试:

( 1 ) 仅在电源线上加磁环,测试结果:改善不明显;

( 2 ) 仅在USB 线上加磁环,测试结果:改善仍然不明显;

( 3 ) 在USB 线和电源线都加磁环,测试结果:改善较明显,干扰频点整体有所下降。

从上可得,干扰频点是从两个接口带出来的,并非是电源接口或USB 接口的问题,而是内部干扰频点耦合到这两个接口所导致的,仅屏蔽某一接口不能解决问题。

经过近场量测发现,干扰频点来之于核心控制板的一个32.768KHz 的晶振,产生很强的空间辐射,使得周围的走线和GND 都耦合了32.768KHz 谐波杂讯,再通过接口USB 线和电源线耦合辐射出来。而该晶振的问题在于以下两点问题所导致的:

( 1 ) 晶振距离板边太近,易导致晶振辐射杂讯。

( 2 ) 晶振下方有布信号线,,这易导致信号线耦合晶振的谐波杂讯。

( 3 ) 滤波器件放在晶振下方,且滤波电容与匹配电阻未按照信号流向排布,使得滤波器件的滤波效果变差。

三、解决对策

根据分析得出以下对策:

(1)晶体的滤波电容与匹配电阻靠近CPU 芯片优先放置,远离板边;

(2)切记不能在晶体摆放区域和下方投影区内布地;

(3)晶体的滤波电容与匹配电阻按照信号流向排布,且靠近晶体摆放整齐紧凑;

(4)晶体靠近芯片处摆放,两者间的走线尽量短而直。

可以参考如下图布局方式:

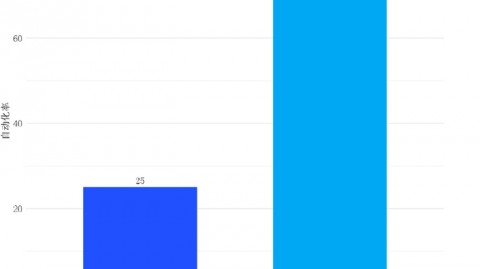

经整改后,样机测试结果如下:

四、结论

现今很多系统晶振现今很多系统晶振时钟频率高,干扰谐波能量强;干扰谐波除了从其输入与输出两条走线传导出来,还会从空间辐射出来,若布局不合理,容易造成很强的杂讯辐射问题,而且很难通过其他方法来解决,因此在PCB 板布局时对晶振和CLK 信号线布局非常重要。

晶振的PCB设计注意事项

(1) 耦合电容应尽量靠近晶振的电源引脚,位置摆放顺序:按电源流入方向,依容值从大到小依次摆放,容值最小的电容最靠近电源引脚。

(2) 晶振的外壳必须接地,可以晶振的向外辐射,也可以屏蔽外来信号对晶振的干扰。

(3) 晶振下面不要布线,保证完全铺地,同时在晶振的300mil范围内不要布线,这样可以防止晶振干扰其他布线、器件和层的性能。

(4) 时钟信号的走线应尽量短,线宽大一些,在布线长度和远离发热源上寻找平衡。

(5) 晶振不要放置在PCB板的边缘,在板卡设计时尤其注意该点。

PCB上晶振布局很难?5分钟教你掌握

1、问题描述

某行车记录仪,测试的时候要加一个外接适配器,在机器上电运行测试时发现超标,具体频点是84MHZ、144MH、168MHZ,需要分析其辐射超标产生的原因,并给出相应的对策。辐射测试数据如下:

2、辐射源头分析

该产品只有一块PCB,其上有一个12MHZ的晶体。其中超标频点恰好都是12MHZ的倍频,而分析该机器容易EMI辐射超标的屏和摄像头,发现LCD-CLK是33MHZ,而摄像头MCLK是24MHZ;

通过排除发现去掉摄像头后,超标点依然存在,而通过屏蔽12MZH晶体,超标点有降低,由此判断144MHZ超标点与晶体有关,PCB布局如下:

3、辐射产生的原理

从PCB布局可以看出,12MHZ的晶体正好布置在了PCB边缘,当产品放置与辐射发射的测试环境中时,被测产品的高速器件与实验室中参考接地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;

而寄生电容实质就是晶体与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越大,晶体在PCB边缘与在PCB中间时电场分布如下:

(PCB边缘的晶振与参考接地板之间的电场分布示意图)

(PCB中间的晶振与参考接地板之间的电场分布示意图)

从图中可以看出,当晶振布置在PCB中间,或离PCB边缘较远时,由于PCB中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地之间,即在PCB内部,分布到参考接地板去的电场大大减小,导致辐射发射就降低了。

4、处理措施

将晶振内移,使其离PCB边缘至少1cm以上的距离,并在PCB表层离晶振1cm的范围内敷铜,同时把表层的铜通过过孔与PCB地平面相连。经过修改后的测试结果频谱图如下,从图可以看出,辐射发射有了明显改善。

5、思考与启示

高速的印制线或器件与参考接地板之间的容性耦合,会产生EMI问题,敏感印制线或器件布置在PCB边缘会产生抗扰度问题。

如果设计中由于其他一些原因一定要布置在PCB边缘,那么可以在印制线边上再布一根工作地线,并多增加过孔将此工作地线与工作地平面相连。

相关问答